关键字:光栅-笔划;视频;DSP;FPGA

Luan Chun-Xu , Chen Xiao-Chuan, Yi Xiao-Qing

Abstract:The characteristic of raster-stroke signal is described. The hardware design proposal based on TMS320- DM642 DSP + XC2S100E FPGA is proposed. The key techniques about cache allocation of conversion system are discussed. After the operation principle of the conversion system is described, the design proposal of the subsidiary devices FPGA is elaborated and the software flow of the key devices DSP is presented. The practice shows that the system has feasibility and reliability.

Key words:Raster-Stroke; Video; DSP; FPGA

0 引言

光栅-笔划视频信号已广泛应用于现代军、民用机载电子设备上[3]。光栅-笔划视频信号在空间上采用叠加方式,笔划扫描出字符画面, 紧接着光栅扫描出图像, 二者显示在同一视野区域内[4]。信号的总线数为5根,包括X(X方向扫描信号),Y(Y方向扫描信号),Z(笔划亮灭信号),V(光栅亮灭信号),M(视频波门信号,光栅与笔划的分段标识),光栅视频信号由X,Y,V构成,笔划视频信号由X,Y,Z构成,这五个信号之间有严格的同步关系。

祝俊等人已用复杂CPLD实现笔划到光栅的转换系统,但是由于输入的模拟信号变化率快,加之叠有噪声等因素,若只做简单的制式变换会出现图像模糊,蠕动,字符扭曲等现象。因此,我们设计了基于TMS320DM642 DSP的转换系统,该系统已成功应用于机载设备中,具有更好的清晰度和更好的抗干扰能力。

1 系统结构及工作原理

1.1 系统结构设计

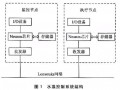

该系统主要实现48FPS(帧/秒)混合视频信号到60FPS LCD数字信号的转化及优化显示功能。系统原理框图如图1所示。系统主要采用TI公司生产的TMS320 DM642 DSP,Xilinx公司生产的XC2S100E FPGA及Linear公司生产的LTC1420 A/D等芯片。

TMS320 DM642 DSP是TI公司于2003年推出的面向视频/图像处理的高性能定点DSP芯片,指令执行速度高达5760 MIPS,具有8个高性能独立的功能单元,64Bit EMIF可支持1024MByte空间,无缝连接异步存储器SRAM和EPROM,同步存储器SDRAM和SBSRAM。并且存储器之间及存储器和外设之间的数据交换可以通过EDMA快速完成。XC2S100E FPGA是Xilinx公司SpartanⅡ系列产品,支持高达200Mhz的处理速度,具有202个I/O,38,400bit Distribute RAM,40K Bits Block RAM。

LTC1420 是一10Msps,12bit A/D转换芯片。MT48LC4M32B2是4M 32bit芯片,最高支持166 MHz。Am29LV160D是2 M x 8Bit芯片,访问速度最快可达到70ns。

图1 系统原理框图

1.2系统工作原理

1.2.1系统缓冲设计

该视频信号转换系统属于实时系统,缓冲分配是系统设计的关键部分。采用缓冲主要有两个目的,一是为提高据总线利用率,二是减小CPU与外存储器速度差所造成的影响。系统主要以双缓冲和四缓冲为主。双缓冲以乒乓方式工作,在同一时刻,一个为读缓冲,另一个为写缓冲;四缓冲以循环方式工作,缓冲读取依次由A到D进行,缓冲写入也是依次由A到D进行,缓冲数据更新通过标识量判断,当缓冲数据被读走后,缓冲将转为写缓冲刷新其中数据。系统缓冲结构如图2所示。从功能角度看,系统主要包括四类缓冲。第一类是视频数据的采样缓冲,主要包括FPGA中的AD_FIFO,DSP中的视频采样处理双缓冲A和B。FPGA中的FIFO对经A/D采样后的视频信号进行缓冲,在A/D采样和DSP间加入FIFO是为了减少DSP数据总线负担,实现数据批量传输,提高DSP数据吞吐量;DSP中的采样双缓冲属于软缓冲,双缓冲功能交替通过标识量进行控制,当一个缓冲接受FPAG数据时,另一缓冲数据正被视频处理模块读取,采样双缓的使用避免了写入和读取冲突,实现了实时处理采样数据的功能。第二类是视频图像形成双缓冲A和B,采样后的原始视频信号经过滤波等处理后,送入内部数字图像形成缓冲中,这两个缓冲分别存有一幅数字图像,使用双缓既可完成视频数据重组,实现扫描转换,又可防止数据读写冲突,这两个缓冲也是乒乓方式工作模式,一个缓冲在形成的图像数据时,另一个缓冲正在向SDRAM中发送的图像数据。第三类是视频图像发送缓冲,缓冲中存储的是转换后的视频数据,由于输入48FPS与输出60FPS存在速率差,也即SDRAM的读取速率大于写入速率, 系统中采用的SDRAM四缓冲可防止这种速度差读写冲突,实现慢帧率到快帧率的转换。第四类是LCD出口显示缓冲,LCD FIFO是数字视频信号出口硬缓冲,在SDRAM与LCD之间设置LCD FIFO主要是减小它们之间速度差异所产生的影响。

图2 缓冲结构图

1.2.2系统工作原理

X,Y,Z,V四路模拟信号首先经过AD813调理电路后以差分形式输入到LTC 1420 A/D转换芯片,经该芯片的采样将模拟视频信号转换为数字视频信号,采样后的数字视频信号与M信号组成32位视频信号送入FPGA解码,滤波,同步后,缓冲到FPGA AD FIFO中。当FIFO中的数据达到半满时,FIFO向DSP发送半满信号,触发EDMA事件,EDMA将FIFO中包含200个数据的EDMA帧读出,存储到DSP A/D双缓冲中的写入缓冲中。DSP从DSP A/D缓冲读取视频信号进行滤波等处理,处理后的数据存入数字图像形成缓冲中重组成视频图像数据。当整幅图像数据形成后,触发EDMA事件,通过EDMA将数字图像数据拆分送到外部SDRAM的写入缓冲中。FPGA LCD FIFO半空时将触发EDMA事件,将SDRAM中以100个数据为EDMA帧的缓冲数据发送到LCD FIFO中,LCD FIFO缓冲后的数据再送到LCD控制器最终在LCD上显示。

2 FPGA设计

FPGA设计采用ISE开发平台,ISE是Xilinx CPLD/FPGA开发平台,该平台集成有十几个辅助设计软件,支持原理图,VHDL,VerilogHDL输入。从逻辑设计到最终配置文件生成及FPGA加载均可在该平台上完成。开发过程中利用ISE提供的免费IP核和逻辑仿真软件加快了原理逻辑设计速度。调试时采用在线逻辑分析仪ChipScope Pro方便了系统调试,缩短了系统开发周期。

系统FPGA原理框图如图3所示。FPGA在该系统中扮演视频信号辅助处理的角色,是外部视频信号接口和DSP的联系纽带,其功能模块主要包括FIR滤波器,输入视频信号解码器,A/D FIFO,LCD FIFO,输出视频信号解码器,LCD控制电路等。

图3 FPGA原理框图

图3左侧输入的X,Y,V,Z,M是经A/D输出的数字视频信号,X,Y进入FPGA后经过FIR低通滤波器及解码器转换为数字图像的坐标点,为保证X,Y,Z,V,M五路信号的同步关系,Z,V,M信号需经延时电路。变换及延时后的信号组合成32位数据存放到AD FIFO中,FIFO半满时,AD FIFO向DM642产生FIFO半满事件。

图3右侧的LCD FIFO主要缓冲输出视频流,缓冲中的视频数据经输出视频信号解码器后与LCD时序产生电路产生的HS,VS,DE及CLK同步输出到LCD。

3 系统软件设计

DM642软件主要由应用程序和DSP/BIOS嵌入式操作系统组成,主要完成FPGA配置,视频图像滤波,图像矩阵形成及外设间协调等功能。

DM642主程序流程图如图4所示。系统程序及FPGA的配置文件存储在FLASH中,上电后DSP从FLASH加载系统程序,并配置FPGA。初始化所有外设及缓冲区后使能A/D及LCD驱动,系统开始协同运作。

图4 系统主程序流程图

系统中数据传输无需DSP参与由EDMA独自完成,EDMA完成A/D FIFO到DSP内部A/D双缓(记为AD_EDMA),内部数字图像双缓到SDRAM四缓(记为SDRAM_EDMA)及SDRAM四缓到LCD FIFO(记为LCD_EDMA)三部分数据传输,并分别产生EDMA中断。EDMA中断处理程序流程图如图5所示,在EDMA中断处理程序中,首先根据EDMA通道标识,对各种类型的EDMA中断进行判断。若为AD_EDMA中断,则切换A/D双缓并触发AD软中断,AD软中断程序主要完成对刚写入的A/D采样数据进行区分,即判断哪些是笔划信号,哪些是光栅信号;若为SDRAM_EDMA中断则触发SDRAM软中断。若为LCD_EDMA中断则更改LCD_EDMA源地址。

SDRAM软中断程序流程图如图5所示,在SDRAM软中断中首先判断一帧图像是否传输完毕,如果传输完毕则切换DSP发向SDRAM的四缓,即改变SDRAM_EDMA的目的缓冲地址;否则继续发送上一帧图像。

A/D处理任务程序框图如图5所示,在处理任务中首先检查A/D采样缓冲区中的数据是光栅信号还是笔划信号,若是笔划信号则进行特殊的数字滤波处理并转化为数字图像添加到数字图像矩阵中;若是光栅信号则直接向数字图像矩阵中填充。处理完成后触发SDRAM_EDMA,向SDRAM发送准备好的图像数据,若没有准备好则不发送.

图5 系统子程序流程图

4 系统验证

经现场调试,系统可以正确显示测试图像,无抖动,蠕动等现象,而且在输入信号上进行人工加扰时,对系统的显示没有明显影响,已满足设计需求及工程应用。

结束语

文章设计并实现了基于DM642视频信号转换系统。详细阐述了系统工作原理,FPGA设计方案。实践证明图像显示正确,稳定,清晰,受噪声干扰小,满足工程应用。该系统的实现对视频转换领域的应用有一定的参考价值。

参考文献:

[1] 陈青华,谢晓方,高 波. 多功能显示模拟器的设计与实现[J].《火力与指挥控制》第32卷,第8期 2007年8月. 110-112.

[2] 来跃深,尚雅层,宋方林,刘方,陈晓. 用追赶法实现光栅—笔划兼容扫描[J].《电子技术应用》2005年 第11期.55-57.

[3] 祝俊, 林祖伦, 张义德, 杨健君. 随机扫描到光栅扫描转换系统的研究[J].《电子科技大学学报》 2005 年12月 第34卷 第6期.783-785.

[4] TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor SPRS200J–JULY 2002–REVISED[Z] AUGUST 2005,http://www.t i.com .

[5] TMS320C6000 DSP External Memory Interface (EMIF) Reference Guide Literature Number: SPRU266E February[Z] 2006,http://www. ti.com .

[6] Spartan-IIE 1.8V FPGA Family: Complete Data SheetDS077[Z] July 28, 2004,http://www.xilinx. com .